一个陶瓷电容会因其构造而产生各种阻抗、感抗,比较重要的就是ESR等效串联电阻及ESL等效串联电感—这就是容抗的基础,其中ESR是等效串联电阻,ESL是等效电感。等效电感在去耦陶瓷电容中太高的话食不行的,那么要降低效电感才行。

去耦陶瓷电容的ESL是由于内部流动的电流引起的,使用多个去耦陶瓷电容并联的方式可以降低电容的ESL影响,而且将两个去耦电容以相反走向放置在一起,从而使它们的内部电流引起的磁通量相互抵消,能进一步降低ESL,此方法适用于任何数目的去耦电容。

同时去耦陶瓷电容可以用不同容值组合:在去耦电容的设计上,通常采用几个不同容值(通常相差二到三个数量级,如0.1uF与10uF),基本的出发点是分散串联谐振以获得一个较宽频率范围内的较低阻抗。

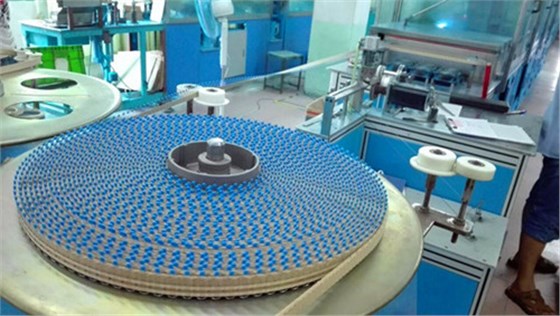

如您还有其它技术上的疑问可联系我们,我们竭力为您解决。东莞市智旭电子制造安规电容,高压薄膜电容,独石电容,压敏电阻,薄膜电容,更多品质电容尽在JEC。可以免费提供样品测试,期待您的莅临。以上资讯来自东莞市智旭电子有限公司研发部提供,更多资讯请大家移步网站中智旭资讯中获取。

CBB13电容 102K 250V薄膜电容

CBB13电容 102K 250V薄膜电容 CBB81电容 102K 1600V薄膜电容

CBB81电容 102K 1600V薄膜电容 CBB电容 CL21X 224K 250V薄膜电容

CBB电容 CL21X 224K 250V薄膜电容 CBB21S 104K 450V薄膜电容

CBB21S 104K 450V薄膜电容