去耦陶瓷电容的选择

去耦,专指去除芯片电源管脚上的噪声。该噪声是芯片本身工作产生的。 在直流电源回路中,负载的变化也会引起电源噪声,去耦的基本方法是采用去耦陶瓷电容,而去耦电容一般选择陶瓷电容。那么去耦陶瓷电容怎样选择呢?下面和大家浅谈浅谈。

在高速时钟电路中,尤其要注意元件的RF去耦问题,这主要是因为元件会把一部分量耦合到电源/地系统之中,然后这些量以共模或差模RF的形式传播到其它部件中。陶瓷片电容需要比时钟电路要求的自激频率更大的频率,这样可选择一个自激频率在10~30 MHz,边沿速率是2 ns或者更小的电容。

由于许多PCB的自激范围是200~400 MHz,当把PCB结构看做一个大电容时,可以选用适当的去耦陶瓷电容,增强EMI的抑制。我们可以知道由于引线中不可避免存在较小电感,表面安装元件具大约两个数量级的自激频率。

由实际经验可知,选择不同去耦电容的依据,通常是根据时钟或处理器的一谐波来选择。但是,町电流是由3次或5次谐波产生的,此时就应该考虑这些谐波,采用较大的分立陶瓷电容去耦。在达到200~300 MHz以上频率的电流工作状态后,0.1μF与0.01μF并联的去耦电容由于感性太强,转换速度缓慢,不能提供满足需要的充电电流。

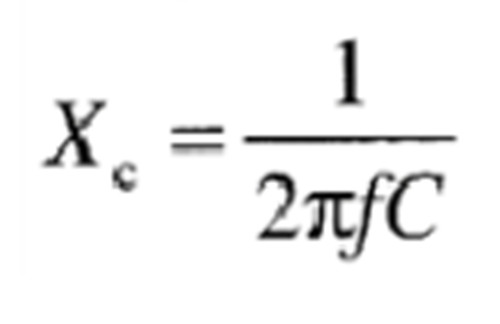

在PCB上放置元件时,须提供对高频RF的去耦。须确保所选去耦电容能满足可能的要求。考虑自激频率的时候需要考虑对重要谐波的抑制,一般考虑到时钟的5次谐波。对去耦电容容抗的计算是选择去耦电容的基础,表示为其中,Xc是容抗(Ω);f是谐振频率(Hz);C为电容大小。选择去耦陶瓷电容的关键是计算所用电容的容值大小。

电容容抗的计算是选择去耦电容的基础,Xc是容抗(Ω);f是谐振频率(Hz);C为电容大小。选择去耦陶瓷电容的关键是计算所用电容的容值大小。

如您还有其它技术上的疑问可联系我们,我们竭力为您解决。东莞市智旭电子制造安规电容,高压陶瓷电容,独石电容,压敏电阻,薄膜电容,更多品质电容尽在JEC。可以免费提供样品测试,期待您的莅临。以上资讯来自东莞市智旭电子有限公司研发部提供,更多资讯请大家移步网站中智旭资讯中获取。

最新产品

同类文章排行

- 薄膜电容中之CBB电容和CL电容有何差异?

- 带你认识超级电容的“V”和“F”

- 压敏电阻起火和天干物燥有关系吗?

- 陶瓷电容过压使用会有什么影响?

- 智能马桶起火原来是因为这个!

- 减少薄膜电容误差:优化电子产品质量的关键

- 【智旭电子】关于超级电容的一些小科普

- 压敏电阻参数不对会对电子产品产生什么影响?

- 什么是温度特性?不同类型的陶瓷电容温度特性有何不同?

- 什么是暖菜板?暖菜板中的热敏电阻

最新资讯文章

您的浏览历史