电源减少噪音原理-电源保护者安规电容

在电源电路中,旁路和退耦都是为了减少电源噪声。旁路主要是为了减少电源上的噪声对器件本身的干扰(自我保护);退耦是为了减少器件产生的噪声对电源的干扰(家丑不外扬)。有人说退耦是针对低频、旁路是针对高频,我认为这样说是不准确的,高速芯片内部开关操作可能高达上GHz,由此引起对电源线的干扰明显已经不属于低频的范围,为此目的的退耦电容同样需要有很好的高频特性。本文以下讨论中并不刻意区分退耦和旁路,认为都是为了滤除噪声,而不管该噪声的来源。

简单说明了旁路和退耦之后,我们来看看芯片工作时是怎样在电源线上产生干扰的。我们建立一个简单的IO Buffer模型,输出采用图腾柱IO驱动电路,由两个互补MOS管组成的输出级驱动一个带有串联源端匹配电阻的传输线(传输线阻抗为Z0)。

设电源引脚和地引脚的封装电感和引线电感之和分别为:Lv和Lg。两个互补的MOS管(接地的NMOS和接电源的PMOS)简单作为开关使用。假设初始时刻传输在线各点的电压和电流均为零,在某一时刻器件将驱动传输线为高电平,这时候器件就需要从电源管脚吸收电流。在时间T1,使PMOS管导通,电流从PCB板上的VCC流入,流经封装电感Lv,跨越PMOS管,串联终端电阻,然后流入传输线,输出电流幅度为VCC/(2×Z0)。电流在传输线网络上持续一个完整的返回(Round-Trip)时间,在时间T2结束。之后整个传输线处于电荷充满状态,不需要额外流入电流来维持。当电流瞬间涌过封装电感Lv时,将在芯片内部的电源提供点产生电压被拉低的扰动。该扰动在电源中被称之为同步开关噪声(SSN,Simultaneous Switching Noise;SSO,Simultaneous Switching Output Noise)或Delta I噪声。

在时间T3,关闭PMOS管,这一动作不会导致脉冲噪声的产生,因为在此之前PMOS管一直处于打开状态且没有电流流过的。同时打开NMOS管,这时传输线、地平面、封装电感Lg以及NMOS管形成一回路,有瞬间电流流过开关B,这样在芯片内部的地结点处产生参考电平点被抬高的扰动。该扰动在电源系统中被称之为地弹噪声(Ground Bounce,我个人读着地tan)。

实际电源系统中存在芯片引脚、PCB走线、电源层、底层等任何互联机都存在一定电感值,因此上面就IC级分析的SSN和地弹噪声在进行Board Level分析时,以同样的方式存在,而不仅仅局限于芯片内部。就整个电源分布系统来说(Power Distribute System)来说,这就是所谓的电源电压塌陷噪声。因为芯片输出的开关操作以及芯片内部的操作,需要瞬时的从电源抽取较大的电流,而电源特性来说不能快速响应该电流变化,高速开关电源开关频率也仅有MHz量级。为了保证芯片附近电源在线的电压不于因为SSN和地弹噪声降低超过器件手册规定的容限,这就需要在芯片附近为高速电流需求提供一个储能电容,这就是我们所要的退耦电容。

所以电容重要分布参数的有三个:等效串联电阻ESR 等效串联电感ESL 、等效并联电阻EPR Rp 。其中重要的是ESR、 ESL,实际在分析电容模型的时候一般只用RLC简化模型,即分析电容的C、ESR、ESL。因为寄生参数的影响,尤其是ESL的影响,实际电容的频率特性表现出阻抗和频率成“V”字形的曲线,低频时随频率的升高,电容阻抗降低;当到低点时,电容阻抗等于ESR;之后随频率的升高,阻抗增加,表现出电感特性(归功于ESL)。因此对电容的选择需要考虑的不仅仅是容值,还需要综合考虑其他因素。

所有考虑的出发点都是为了降低电源地之间的感抗(满足电源大容抗的条件下),在有瞬时大电流流过电源系统时,不于产生大的噪声干扰芯片的电源地引脚。

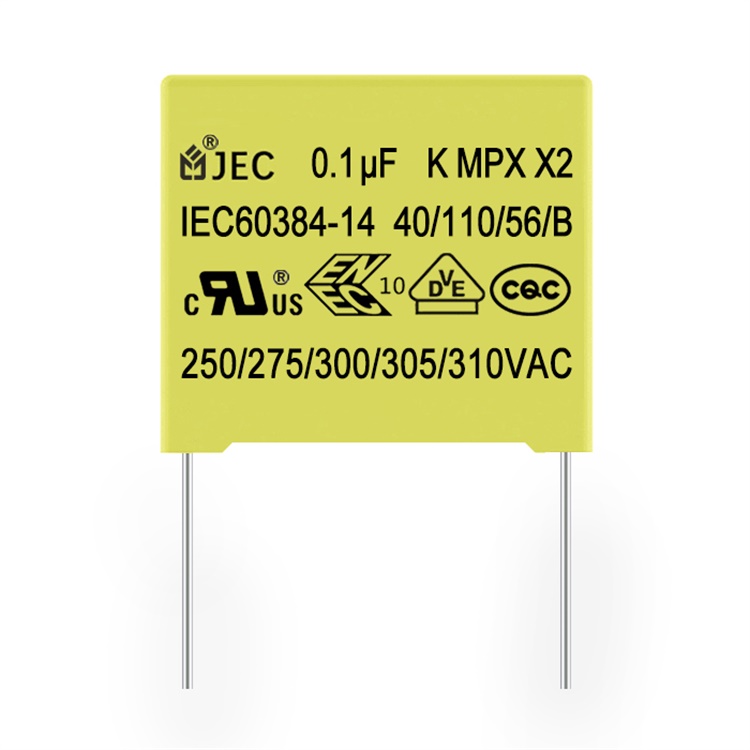

看了以上的电源减少噪音原理-介绍希望能给您带来帮助,科技进步从细节做起,智旭电子专注安规电容生产、研发、销售于一体,品质的体现,如有电源减少噪音方面问题可以提供可靠性解决方案。以上文章由智旭电子提供。

最新产品

同类文章排行

- 冬至来临,南方人过冬法宝:热敏电阻

- 蓝色陶瓷电容和土黄色陶瓷电容

- 【智旭电子】薄膜电容对电子产品的重要性

- 【智旭电子】压敏电阻的发展历程

- 俄罗斯与智旭电子的愉快合作

- 以NTC5D-9为例子教你看懂热敏电阻丝印参数

- 核能充电宝:全球首创陆上模块化小型核反应堆

- 【智旭电子】科技与安规电容

- 没想到它也可以用来制作超级电容

- 用水龙头举例解释压敏电阻的工作原理

最新资讯文章

您的浏览历史